- 半導体ってどうやって作られてるの?

- 製造工程の流れを再確認したい

本記事では、上記の悩みを持つ半導体業界に興味を持ち始めたばかりの方や、半導体業界で働くことになった、これから半導体について学んでいく社会人1年目の方へ向けて半導体製造工程フローをわかりやすく解説していきます。

半導体とは

本来、半導体とは電気をよく通す金属のような”導体”、電気をほとんど通さないゴムのような”絶縁体”の中間の性質をもつシリコンなどの物質や材料のことです。

しかし、ICチップやLSI(Large Scale Integration)と言われる集積回路も”半導体”と呼ばれています。

半導体製造工程とはこの集積回路(IC:Integrated Circuit)を作っていく工程です。

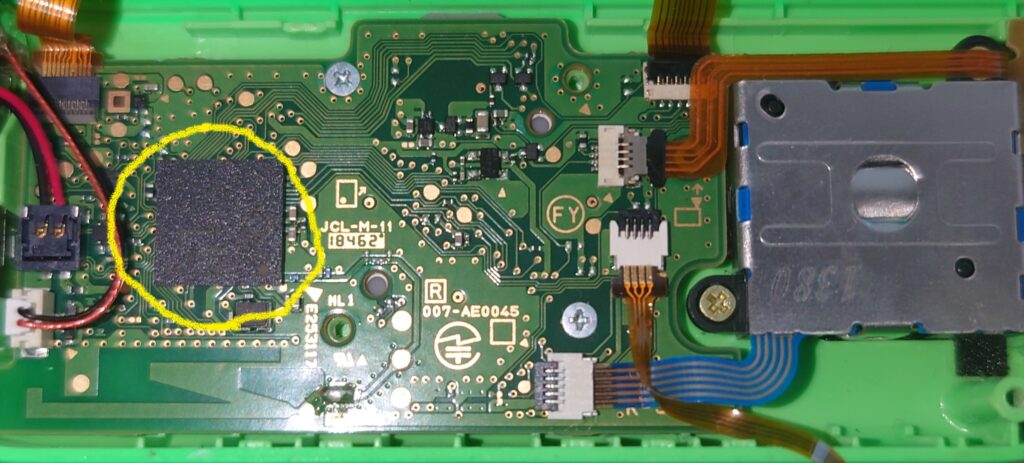

製造工程フローを理解するうえで、完成形があった方がイメージしやすいでしょう。

上の画像はNintendo SwitchのコントローラーであるJoyConの内部の様子です。

黄色で囲まれているものが半導体であり、マイクロコンピュータ(MCU)と呼ばれる様々な機能を一枚の半導体で制御できるものです。

半導体製造工程のフロー

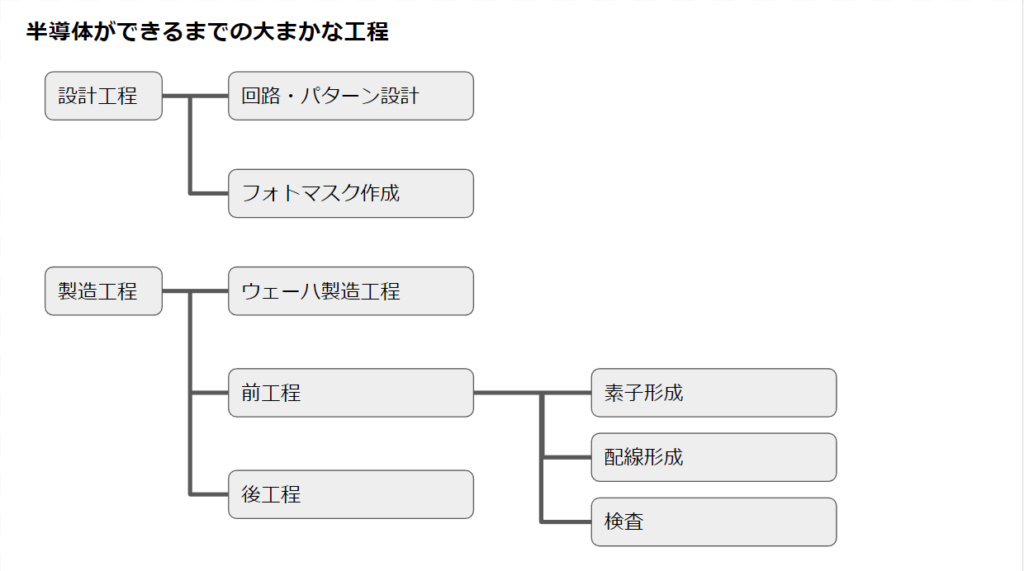

半導体製造フローを最も大きくカテゴリー分けを行うと

- 設計工程

- 製造工程

の2種類に分けられます。

設計工程

どのような機能・性能を持った半導体にするか?半導体製造に向けて準備する工程です。

製造工程

半導体完成までICを作りこんでいく工程です。

設計工程

設計工程は回路・パターン設計、フォトマスク作成とカテゴリー分けができます。

回路・パターン設計

EDAツールを用いて、合成・検証・シミュレーションを繰り返し、論理・回路・パターン・レイアウトの設計を行う。

フォトマスク作成

ウェーハ上に多数のICを作るために、ICのパターンを転写するフォトマスクを作成する。

製造工程

製造工程は大きく分けて三つ。

ウェーハ製造工程、前工程、後工程の3つの工程に分けることができます。

ウェーハ製造工程

シリコンからシリコンウェーハを作る工程

前工程

シリコンウェーハ上に多数のICを作る工程

後工程

シリコンウェーハを一つのICチップとしていく工程

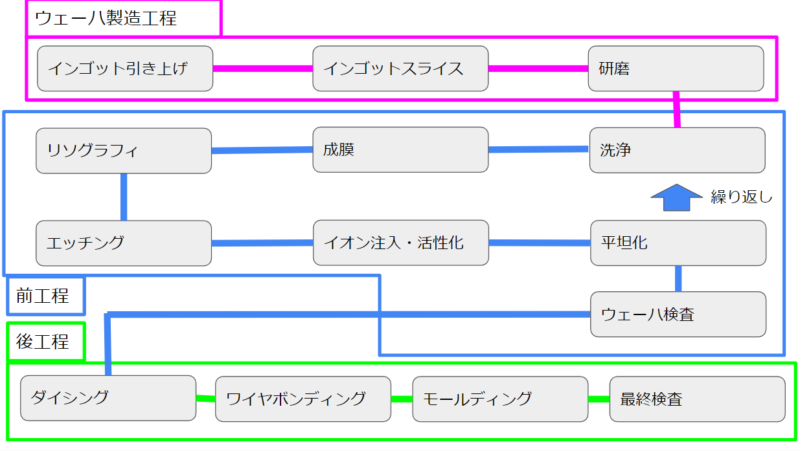

ウェーハ製造工程

現在の半導体材料にもっとも使用されているのがシリコン(ケイ素Si)

パワー半導体と呼ばれる分野では化合物半導体である、SiC、GaNが使われ始めている。

ウェーハ製造工程とは半導体材料からウェーハを作る工程です。

ここではシリコンから作られるシリコンウェーハを前提に開設します。

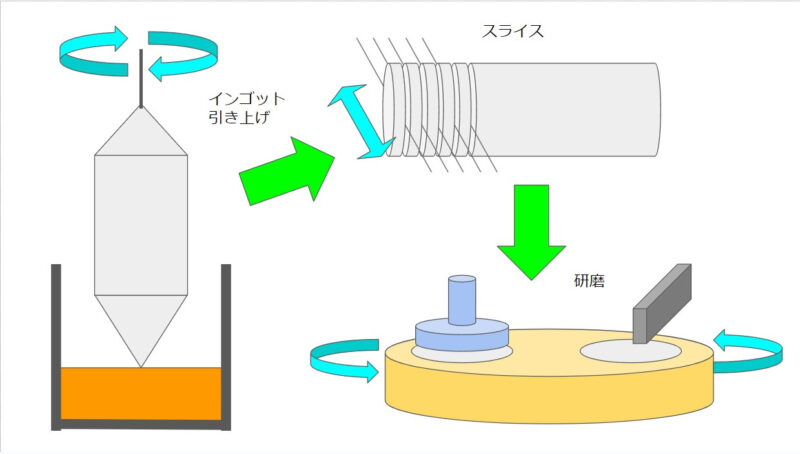

インゴット引き上げ

細かい単結晶のシリコンの粒が集まった超高純度(99.99999999%:イレブンナイン)多結晶シリコンを溶かします。

この融解したシリコンにピアノ線で吊るした単結晶のシリコンを接触させてゆっくり回転させながら引き上げるとインゴット状のシリコン単結晶ができる。

この方法をCZ法(チョクラルスキー法)と呼ぶ。300㎜(12インチ)のサイズまで対応。

FZ法と呼ばれる方法もある。200㎜(8インチ)のサイズまで対応。

スライス(インゴット切断)

インゴットの外周をウェーハ口径に整え、ワイヤーソーでウェーハの厚さに切断する工程。

研磨

ウェーハ上下面の平坦度を整えて、ウェーハ表面の凹凸を取り除くため研磨。

この研磨でウェーハは鏡面状態になり、ポリッシュドウェーハと呼ぶ。

デバイスメーカはダミーウェーハもポリッシュドウェーハが出てくるけど、ウェーハメーカはポリッシュドウェーハではなく、ノンポリッシュウェーハがダミーウェーハとして出てくることもある。

前工程

ここでは半導体の基本構造となるCMOSを例として前工程を解説していきます。

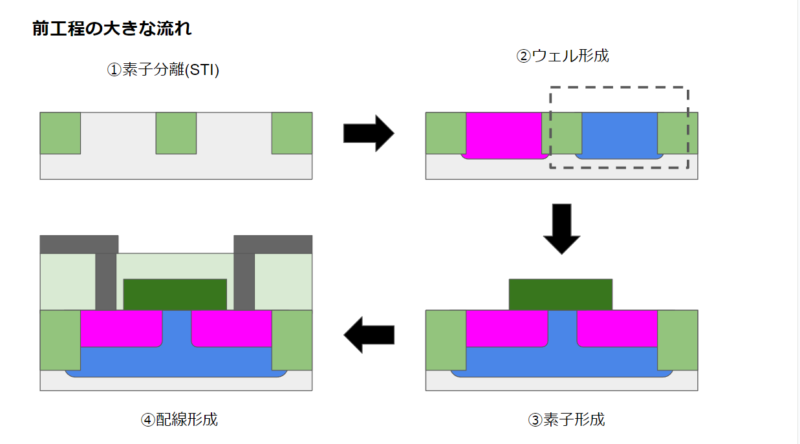

CMOSは大きくわけて4つの工程で分けることができます。

1.素子分離

素子はシリコンウェーハの表面付近に作ります。

各々の素子が独立して動作し互いに干渉しないように分離する工程です。

素子分離の方法はSTI(Shallow Trench Isolation:シャロートレンチアイソレーション)の他にLOCOS(Local Oxidation of Silicon)と呼ばれる方法があります。

2.ウェル形成

ウェルとは井戸の意味。

CMOSにはnMOSとpMOSという2種類のトランジスタを作りこみます。

nMOS作成にはp型不純物(ボロンなど)を打ち込むpウェル

pMOS作成にはn型不純物(リンなど)を打ち込むnウェル

という領域が必要です。その領域づくりの工程です。

3.素子形成

トランジスタなどの素子を作りこんでいく工程です。

いわゆる半導体が半導体として機能するために最も重要な工程です。

素子形成までをFEOL(Front End Of Line)フロントエンドとも呼びます。

4.配線形成

素子形成で作られた多数の素子を相互につなぐ工程です。

半導体の集積度が、素子だけでなく電気的に接続する配線によっても変わるようになり縦方向に配線を積み重ねる多層配線が必要になりました。

配線工程をBEOL(Back End Of Line)バックエンドとも呼びます。

成膜工程

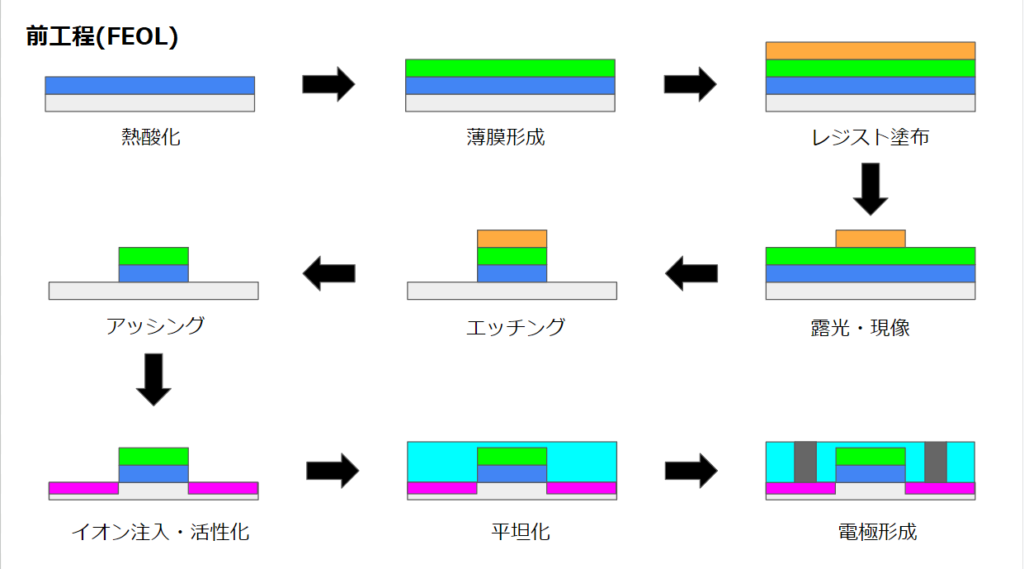

熱酸化

シリコンウェーハを酸素雰囲気の中で高温で処理することで、酸化膜を成長させます。

酸化膜(SiO2)は非常に優れた絶縁膜です。

おおよそ800度以上からウェーハの酸化を促進します。

詳しくは熱処理装置で解説しています。

薄膜形成

半導体膜、絶縁膜、金属膜を形成する工程。

薄膜形成で使われる方法は主に2つ

| CVD | 薄膜の種類に応じて、ガスを熱やプラズマで化学反応で膜を堆積させる。 絶縁膜、半導体膜に使用 |

| スパッタ | 成膜材料をアルゴン原子を高速で衝突させ、付着させて膜を形成。 主に金属膜を付けたいときに使用 |

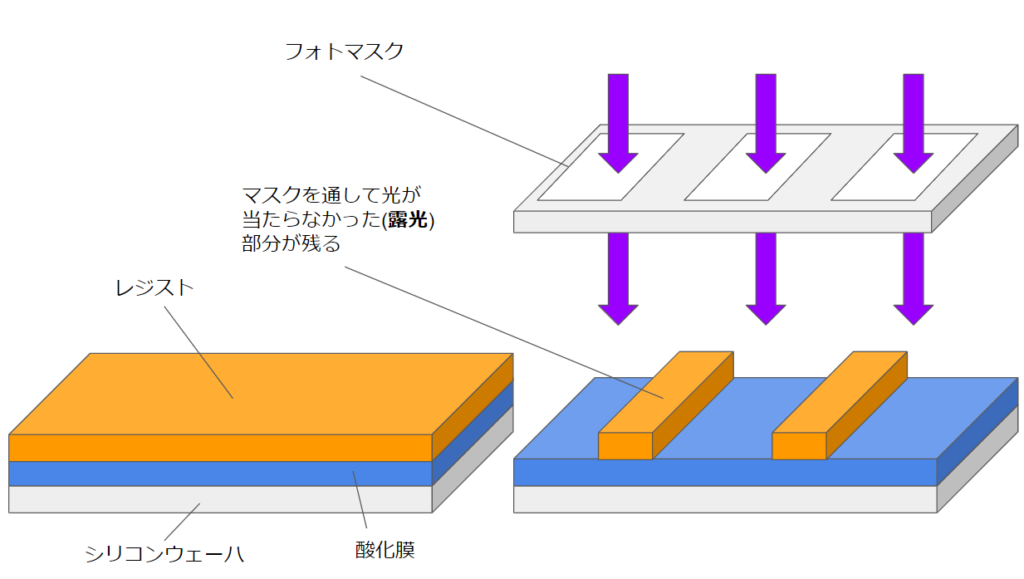

リソグラフィ

フォトレジスト塗布

薄膜の上にフォトレジスト(感光材)を塗布

露光

フォトマスクを通してフォトレジストに光を部分的に照射

現像

露光された部分を除去し、フォトマスクのパターンを転写する。

エッチング

エッチング

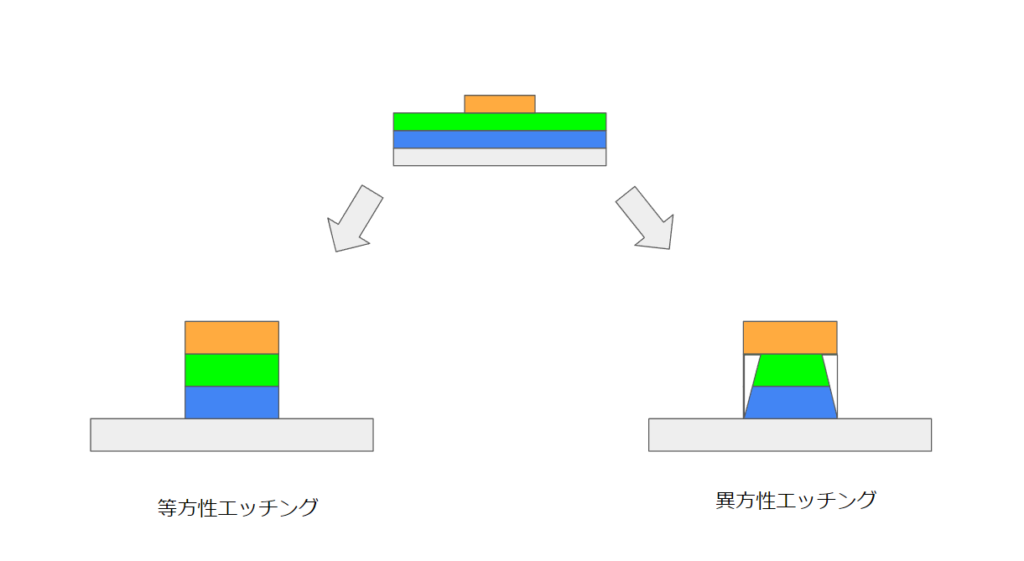

パターン形成されたレジストをマスクにして、薄膜を除去してパターンを形成する工程。

ここでのエッチングはドライエッチングのことで、他にウェットエッチングも存在します。

| ドライエッチング | レジストをマスクにして薄膜を反応性ガス、イオン、ラジカルなどで部分的に除去しパターンを形成。 |

| ウェットエッチング | 液体を用い、材料薄膜を全面あるいはマスクを用いて部分的に除去。 |

等方性エッチングと異方性エッチングがある。

レジスト剥離(アッシング)

エッチング終了後の不要になったレジストを酸素のプラズマで除去する工程。

アッシングは”灰化”とも呼ばれる。

イオン注入・活性化

イオン注入

イオン注入機を用い、リンやボロンなどの不純物イオン(ドーパント)をウェーハに打ち込む工程。

真性半導体であるシリコンはドーパントが存在しないと電気が流れない。

イオン注入されたウェーハはインプラウェーハと呼ばれる

活性化

整った原子配列をもつシリコン(Si)に無理やり不純物イオンを打ち込んだため、原子配列が乱れている。

1000℃程度で熱処理することにより、不純物をシリコン結晶格子上に移動させ(固相拡散)、結晶の回復を行う工程。

詳細は熱処理装置で解説しています。

平坦化

平坦化(CMP)

ICは何層にも重なって形成される。

成膜する際は下地の影響を受けるため、凹凸をなくすためにウェーハ上の絶縁膜や金属膜を研磨して表面を平にする工程。

この工程の後にウェーハを洗浄する洗浄工程が入ります。

電極形成

電極形成(スパッタリング)

ウェーハ表面に電極配線用のAl,Cu,Wなどの金属膜を付ける工程。成膜工程の一部。

ウェーハ検査

プローブ(探針)をウェーハ上のICチップに当てて、良品か不良品か判定する工程。

後工程

ダイシング

ダイシングソーと呼ばれる専用のカッターでウェーハ上のデバイスを個々のICチップに切り分ける工程。

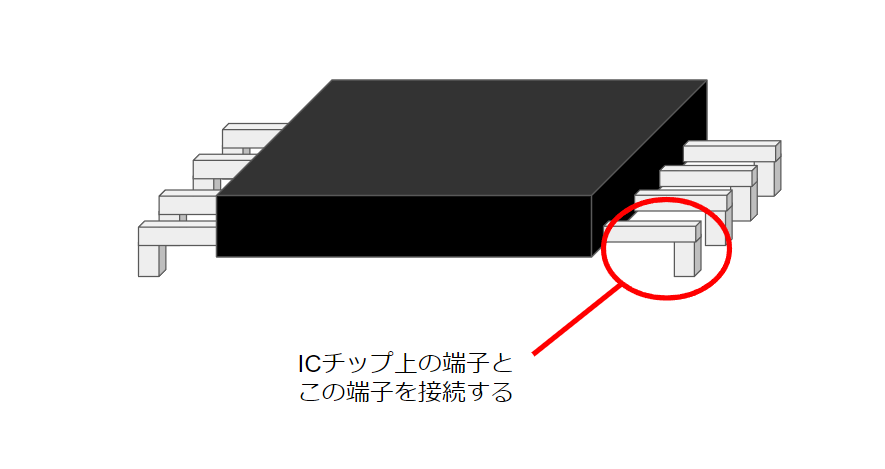

ワイヤボンディング

マウントされたICチップの端子とリード(画像の赤丸)を接続

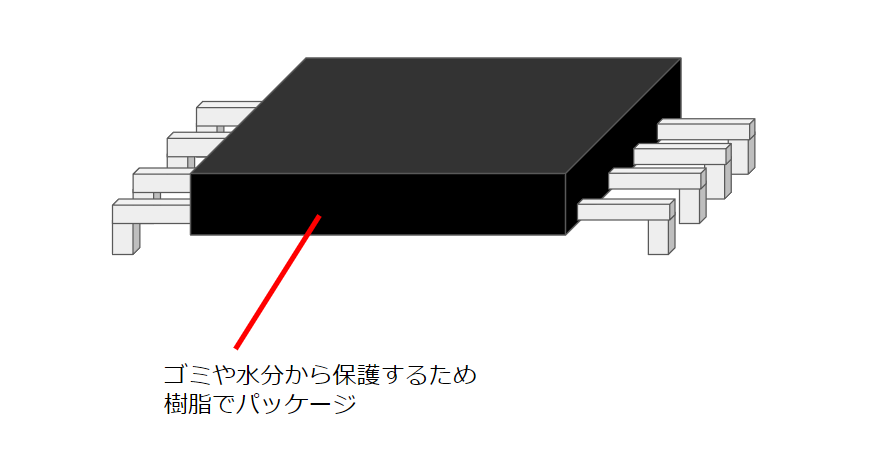

モールディング

ゴミや水分、衝撃から保護するために高温で液状化した樹脂でパッケージ

コメント